奈良先端科学技術大学院大学 情報セキュリティ工学研究室

研究概要

情報セキュリティ確保に関する重要性が日々増大する中、上位レイヤにおけるセキュリティ確保と同様、物理層におけるセキュリティ確保の重要性も高まっています。近年の計測器の高精度化・低価格化、計算機の高速化と記憶装置の大容量化に伴い、従来では技術的に困難だった高度な攻撃の脅威が増大しており、こうした脅威は軍事・外交分野のみならず一般的な商用製品へと拡大しています。

情報セキュリティ工学研究室では、物理層におけるセキュリティに焦点をあて、その情報漏えいのメカニズムとその対策手法の研究開発を行っています。また、物理層のハードウェアを基礎として構成される上位レイヤを含めたシステム全体のセキュリティを確保するための研究も行っています。

漏えい電磁情報によるセキュリティ低下に対する評価・対策技術

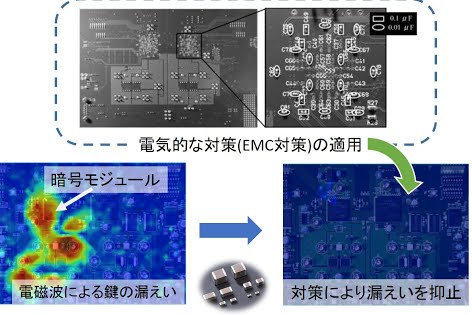

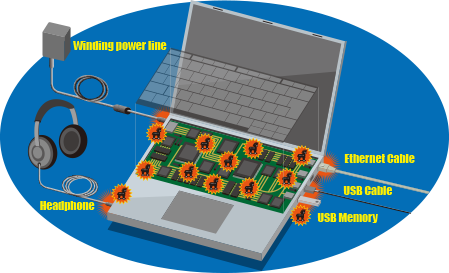

ハードウェアから漏えいする情報によるセキュリティ低下の問題は、これまで暗号モジュールに対するサイドチャネル攻撃やディスプレイ・キーボードなどの入出力デバイスに対するTEMPESTを中心に検討が行われています。これらの脅威は「漏えい電磁情報の計測」と、「計測された情報の解析」からなるため、計測の困難性を高めることでその脅威を抑止できる可能性があります。電磁情報の計測は、電界もしくは磁界をプローブにより検出することで行うことから、プローブが周囲の電磁界を侵襲せずに計測することは物理法則上回避不可能です。即ち、漏えいした電磁情報をプローブにより計測されているか否かを検知できれば、計測の困難性を限りなく高めることが可能となります。本研究室ではこうした計測により生ずる電磁界変化を高精度に広範囲に検知可能なセンサ技術の開発を目指しています。また、攻撃を検知するためには具体的な攻撃手順についても把握が必要となることから、種々のデバイスに対する攻撃手法の評価も行っています。

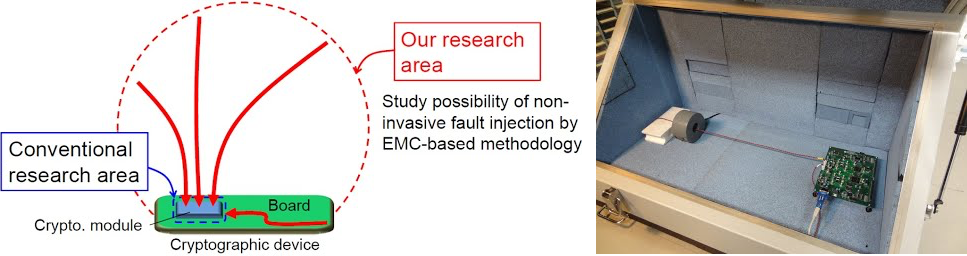

電磁的な外乱によるセキュリティ低下に対する評価・対策技術

ハードウェアへの電磁的な外乱によるセキュリティ低下は、一般的な電子機器に関しては意図的な電磁妨害、特に暗号モジュールに対しては故障利用攻撃と呼ばれ、「故障の注入」と「それにより生じた誤り出力の解析」からなっています。そのため、攻撃の前段となる「故障の注入」を抑止することができれば、その攻撃の多くを無効化できると考えられます。これまで、故障注入にはパルス波や連続正弦波などの電磁信号印加、電源電圧及びクロック操作、レーザーなど照射などが挙げられますが、これらは最終的に機器内部の電気的な外乱を引き起こす事で故障を誘発します。そのため、本研究室では、こうした電気的な変化をチップ内部、基板レベルで検出可能なセンサの開発を行うことで故障注入の抑止を目指すと共に、故障を引き起こす根本原因である電気的な外乱全般をICの内外で検出可能なセンサの開発を行っています。また、攻撃検出の具体的な感度などを決定するためには、実際行われる攻撃を詳細に把握する必要があることから、電磁的な外乱を引き起こす攻撃手順の再現と攻撃手法の評価も行っています。

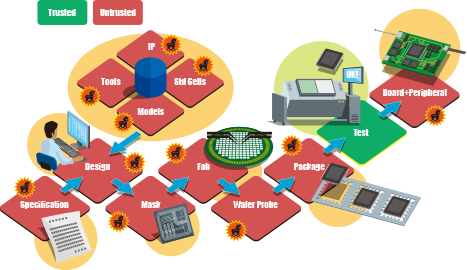

ハードウェア内部回路の意図的な改変によるセキュリティ低下に対する対策技術

ハードウェア内部の回路に対する意図的な改変によるセキュリティ低下は、機器内部に設計者の意図しない電子・電気回路を実装することで、それらをハードウェアトロイとして動作させ、機器内部の機能や仕様の改変、情報の漏えい、機能停止を引き起こします。トロイの実装はIC内部へのゲートや配線追加や基板上への素子や配線の追加などにより行われることから、これらの実装により機器内で変化する電気定数の変化を検出することで、トロイの存在を検知可能となります。そのため、本研究室ではこうしたトロイ実装により変化する機器内部と周囲の電磁界結合度の変化を検出する検査手法を研究開発すると共に、トロイが実装された場合、チップ内部における電気定数が変化することを用いて、機器自体が動作しない様な設計手法の開発を行うと共に、トロイの実装を困難、もしくは実装された後に、非侵襲に短時間で検出する手法についても開発を行っています。また、トロイが攻撃者によって実装されるタイミング、実装コストや攻撃者の能力などをパラメタとした攻撃シナリオについても検討を行っています。

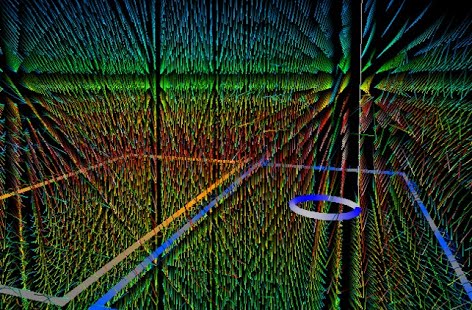

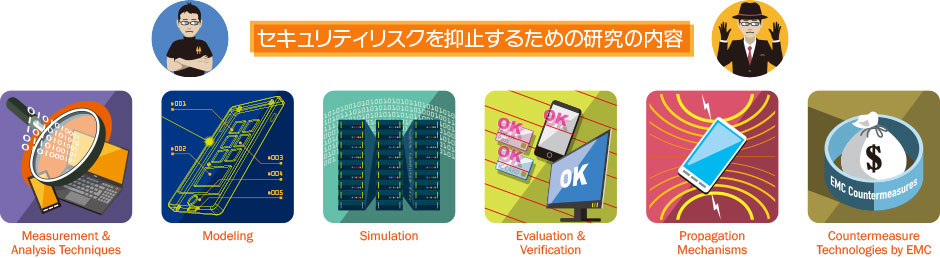

ハードウェアに対する攻撃の可視化及び情報通信システムの信頼性に関する研究

ハードウェア周囲の電磁界を可視化することにより、情報が漏えいするメカニズムの解明及び攻撃者が物理的に回避不可能な対策技術の開発を行っています。また、スーパーコンピュータを用いた大規模な電磁界シミュレーションにより、機器設計時に物理層における攻撃耐性を評価する手法についても研究を行っています。さらに、環境電磁工学(EMC)及び機構デバイス工学の観点から電磁信号の漏えいが少なく、電磁気的な外乱にも耐性のある情報通信システムを構成する機器の設計手法に関する研究を行っています。